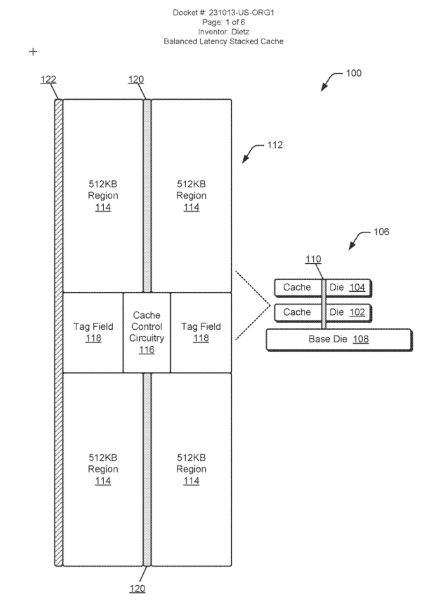

Компания Advanced Micro Devices продолжает искать способы повышения производительности своих процессоров за счет оптимизации подсистемы памяти. В начале 2026 года было опубликовано патентное заявление производителя, описывающее новую архитектуру под названием Balanced Latency Stacked Cache или стекируемый кэш со сбалансированной задержкой. Изобретение направлено на устранение узких мест, возникающих при увеличении объемов кэш-памяти в современных кристаллах.

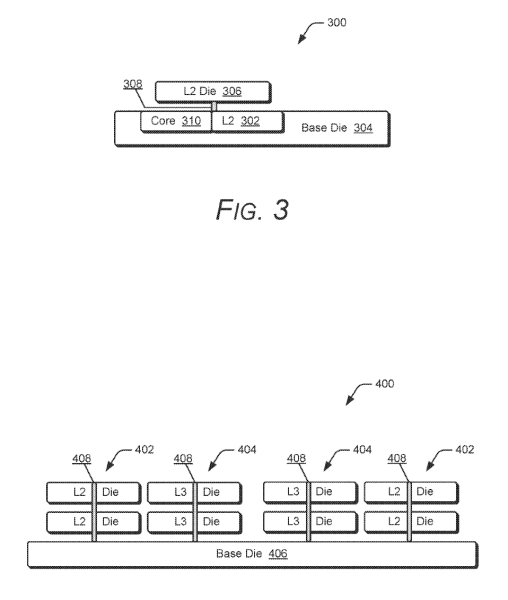

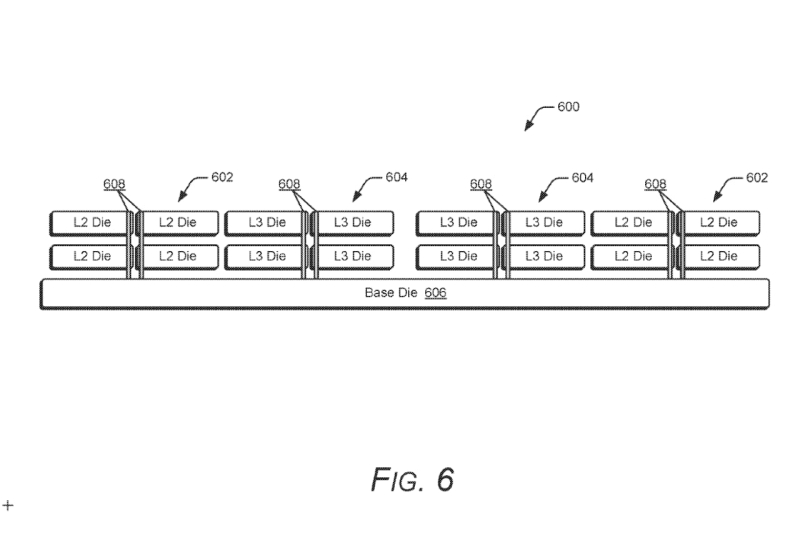

Суть технологии заключается в вертикальном расположении слоев памяти друг над другом с использованием централизованной схемы управления. В отличие от традиционных планарных компоновок, где увеличение объема памяти приводит к удлинению проводников и росту задержек, новая структура использует вертикальные соединительные каналы, проходящие через центр стека. Это позволяет сократить физическое расстояние, которое проходит сигнал от контроллера до ячейки памяти и обратно.

В документе приводится сравнение производительности, где стандартный плоский кэш второго уровня объемом 1 МБ имеет задержку в 14 тактов, тогда как предлагаемая вертикальная структура того же объема выполняет операцию за 12 тактов. Центральное расположение межсоединений обеспечивает равное время доступа к любой части массива данных, устраняя дисбаланс, характерный для растянутых по площади чипов. Такая архитектура позволяет наращивать объем кэша без существенного штрафа к скорости доступа.

Помимо повышения быстродействия, новая компоновка положительно сказывается на энергоэффективности и тепловыделении. Короткие проводники обладают меньшей емкостью и требуют меньше энергии для передачи сигнала. Более быстрая обработка запросов позволяет блокам памяти быстрее переходить из активного режима в режим ожидания, что суммарно снижает потребление энергии и нагрев процессора.

Технология может применяться для различных типов памяти, включая SRAM и DRAM, а также позволяет гибко комбинировать слои кэша L2 и L3. На данный момент неизвестно, в каком поколении процессоров Ryzen или EPYC появится данное решение, однако патент свидетельствует о том, что инженеры AMD активно работают над развитием технологии 3D V-Cache и устранением ее нынешних ограничений.